2t-fn envm with 90 nm logic process for smart card The novel EEPROM cell is based on the Philip's 2T-FN-NOR cell. It features a 2T cell with a select gate at the source side of the floating gate. This source side select gate .

NFC West 2. Dallas Cowboys 12-5 NFC East 3. Detroit Lions 12-5 NFC North 4. Tampa Bay Buccaneers 9-8 NFC South 5. Philadelphia Eagles 11-6 Wild card 6. Los Angeles Rams 10-7 Wild card 7. Green Bay .Find out which teams are winning the 2024 playoff race. Check out the NFL Playoff Picture for the latest team performance stats and playoff eliminations. Learn more.

0 · Sci

1 · Review Non Volatile Floating Gate Flash Memory

2 · Practical Consideration of Endurance and Performance for

3 · Embedded Flash technologies and their applications: Status

4 · Device architecture and reliability aspects of a novel 1.22 μm

5 · A novel EEPROM cell for smart card application

6 · 90nm Node 1T Floating Gate Embedded Flash Memory with

7 · 2T

8 · (PDF) A novel 2

Generic Name: Visiting Cards Corners: Rounded Shape: Rectangle Product Dimensions (lw): 8.5 cm x 5.4 cm Package Dimensions (lwh): 17 cm x 10.5 cm x 2.5 cm Item Weight: 45 g Color Name: White Material: PVC 0.8 mm thickness .

Sci

2T-FN eNVM with 90 nm Logic Process for Smart Card Abstract: We have suggested 2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for .2T-FN eNVM with 90 nm Logic Process for Smart Card Abstract: We have .This question is for testing whether you are a human visitor and to prevent .

This question is for testing whether you are a human visitor and to prevent .

Today in this paper, we present the methodology for endurance and performance enhancement in eNVM (2T-FN) by considering real user mode environment and base-lines in flash IP designing.

The novel EEPROM cell is based on the Philip's 2T-FN-NOR cell. It features a 2T cell with a select gate at the source side of the floating gate. This source side select gate . We have suggested 2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) . We have suggested 2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) and .

2T-FN eNVM with 90 nm Logic Process for Smart Card. 2008 Joint Non-Volatile Semiconductor Memory Workshop and International Conference on Memory Technology and Design. .

The proposed methodology is developed on 1T-Flash NOR cell to reduce area and obtain high performance even at 90nm logic process technology. NOR offers low read .2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) is suggested and demonstrated by 8x8 array .

2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) is suggested and demonstrated by .2T-FN eNVM with 90 nm Logic Process for Smart Card. 2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC .2T-FN eNVM with 90 nm Logic Process for Smart Card Abstract: We have suggested 2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) and demonstrated by 8x8 array cells. The novel EEPROM cell is based on the Philip's 2T-FN-NOR cell. It features a 2T cell with a select gate at the source side of the floating gate. This source side select gate enables low voltage (1.2 V) read operation.

We have suggested 2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) and demonstrated by 8x8 array cells. We have suggested 2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) and demonstrated by 8x8 array cells.

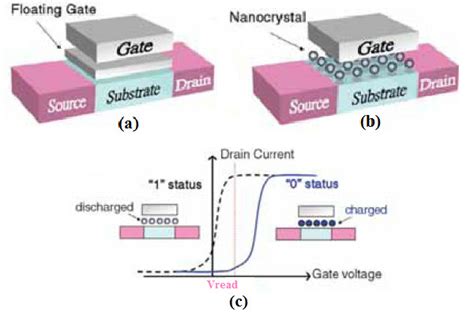

Review Non Volatile Floating Gate Flash Memory

Today in this paper, we present the methodology for endurance and performance enhancement in eNVM (2T-FN) by considering real user mode environment and base-lines in flash IP designing.2T-FN eNVM with 90 nm Logic Process for Smart Card. 2008 Joint Non-Volatile Semiconductor Memory Workshop and International Conference on Memory Technology and Design. doi:10.1109/nvsmw.2008.132T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) is suggested and demonstrated by 8x8 array cells. Expand 11 The proposed methodology is developed on 1T-Flash NOR cell to reduce area and obtain high performance even at 90nm logic process technology. NOR offers low read latencies features; make it suitable choice for direct code execution.

2T-FN eNVM with 90 nm Logic Process for Smart Card. 2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) is suggested and demonstrated by 8x8 array cells.

Data from Infineon’s 90nm generation. FG-based Cells: Flash T-Budget vs. SRAM Functionality. Stronger Flash sidewall oxidation improves endurance, but impacts SRAM yield. Tradeoff between flash reliability and SRAM yield becomes more and more critical with advanced CMOS nodes. Data Source: IFX 90nm generation.2T-FN eNVM with 90 nm Logic Process for Smart Card Abstract: We have suggested 2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) and demonstrated by 8x8 array cells. The novel EEPROM cell is based on the Philip's 2T-FN-NOR cell. It features a 2T cell with a select gate at the source side of the floating gate. This source side select gate enables low voltage (1.2 V) read operation. We have suggested 2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) and demonstrated by 8x8 array cells.

We have suggested 2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) and demonstrated by 8x8 array cells.Today in this paper, we present the methodology for endurance and performance enhancement in eNVM (2T-FN) by considering real user mode environment and base-lines in flash IP designing.

2T-FN eNVM with 90 nm Logic Process for Smart Card. 2008 Joint Non-Volatile Semiconductor Memory Workshop and International Conference on Memory Technology and Design. doi:10.1109/nvsmw.2008.132T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) is suggested and demonstrated by 8x8 array cells. Expand 11 The proposed methodology is developed on 1T-Flash NOR cell to reduce area and obtain high performance even at 90nm logic process technology. NOR offers low read latencies features; make it suitable choice for direct code execution.

2T-FN eNVM with 90 nm Logic Process for Smart Card. 2T-Flash cell design methodology to achieve high performance even at sub-90 nm technology nodes for embedded SOC applications (eNVM) is suggested and demonstrated by 8x8 array cells.

Black Matte PVC | Black Stealth Print | Digital Business Card. €44.99 "Close .

2t-fn envm with 90 nm logic process for smart card|Device architecture and reliability aspects of a novel 1.22 μm